Project information

- Category: Quantum Computing, Quantum Error Correction

- Course: Quantum Information Project

- Location: QuTech, Delft, the Netherlands

- Project date: Nov. 2022 - Jan. 2023

- Promoter: Prof. Dr. Leonardo DiCarlo

- Grade: 10/10

- The report of this project can be shared upon reasonable request.

Abstract

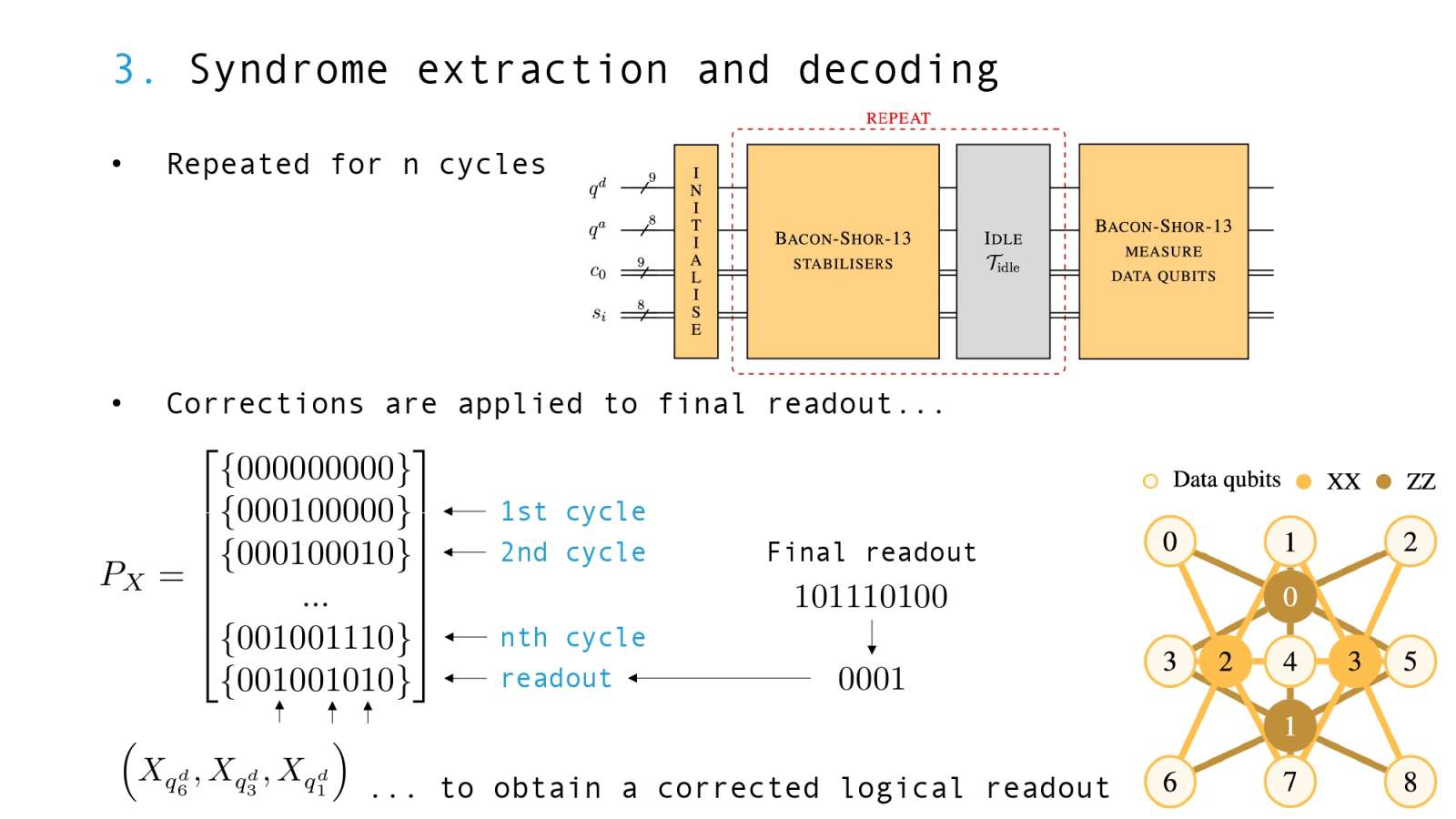

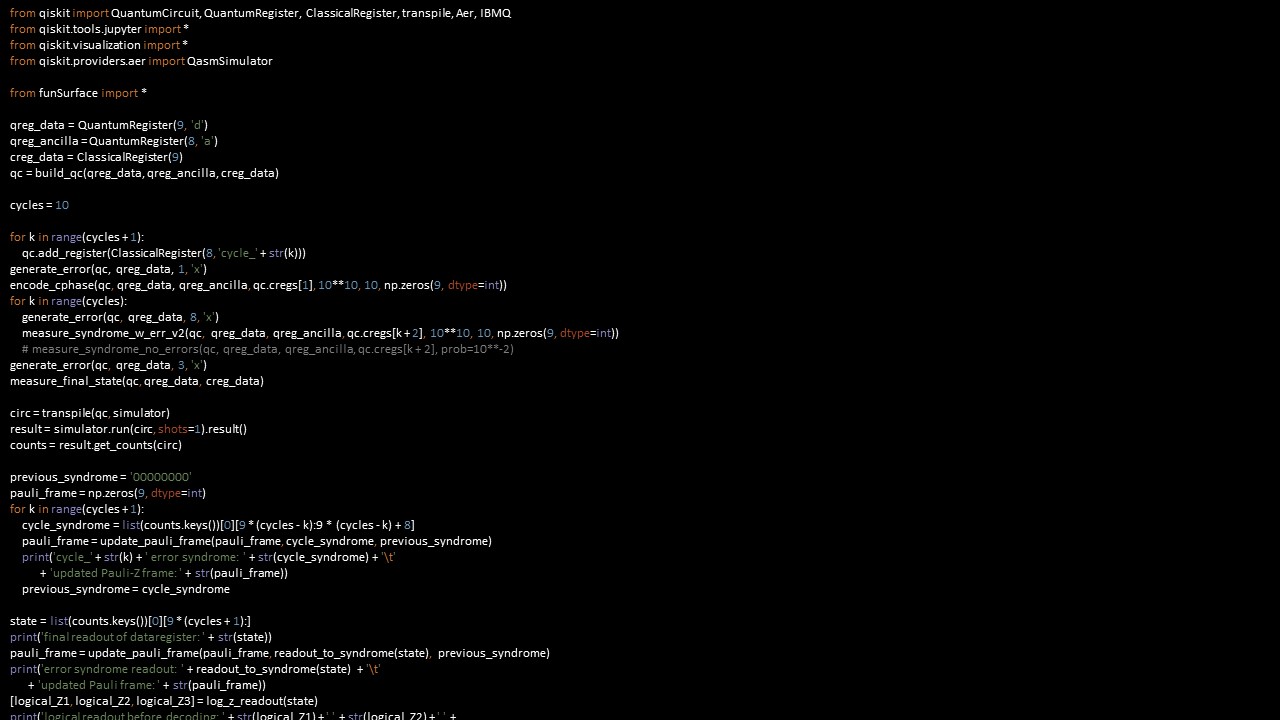

Our self-constructed error model allows us to determine logical error probabilities of Surface-17 and Bacon-Shor-13 in function of relaxation time and error correction cycles. Both parallelised circuits, in native gates of superconducting qubits, reveal a similar logical error rate for high relaxation times, while for low relaxation times, Surface17 outperforms Bacon-Shor-13. The simulation model brings to light that for 50 µs relaxation time the surface code is slightly better than the Bacon-Shor code, although the effects of the number of error correction cycles is comparable for both. The pseudothresholds resulting from our simulations are 750 ns and 60 ns for Bacon-Shor-13 and Surface-17 respectively. At a relaxation time of 100 µs, Bacon-Shor is significantly better. In addition, our simulations indicate that errors on the ancilla register increases the logical error rate as the relaxation time decreases. At a relaxation time of 100 µs and 50 µs, the logical error rate goes up by a factor of 29.03% and 32.78% respectively, at ten rounds of error correction. Fault-tolerant circuits were compared to the logical error rates with a non-fault-tolerant version of Bacon-Shor. A non-fault-tolerant stabiliser order reveals a dramatic increase in logical error rate; about a factor of 1237.5% and 764.69% for 100 µs and 50 µs respectively, at ten cycles of error correction, compared to the fault-tolerant circuit with an imperfect ancilla register. This error rate is worse than that of an idle qubit, proving the importance of fault-tolerant quantum error correction codes in practice.